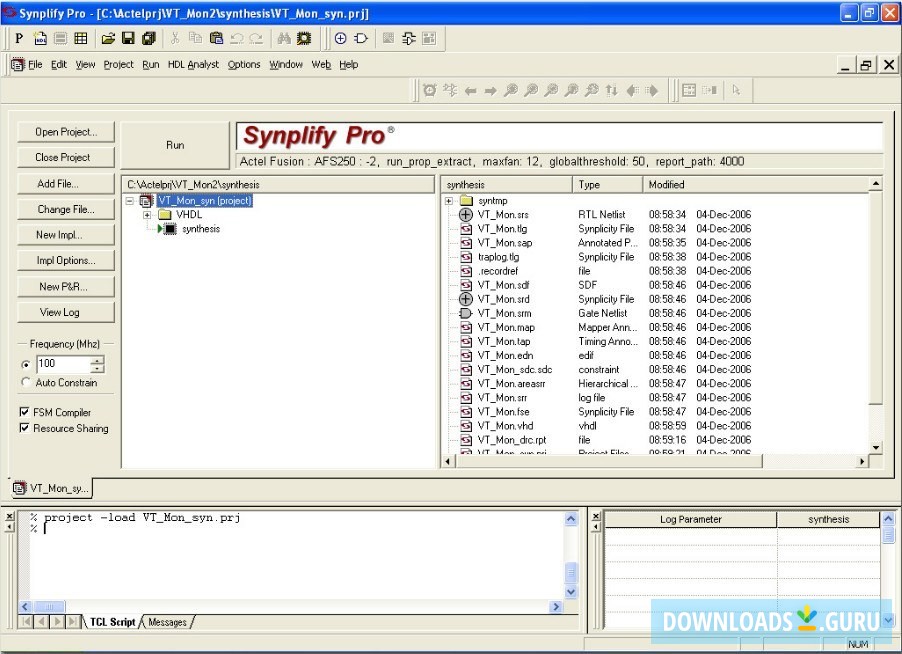

Since 1986, engineers around the world have been using Synopsys technology to design and create billions of chips and systems. As a leader in electronic design automation (EDA) and semiconductor IP, Synopsys delivers software, IP and services to help engineers address their design, verification, system and manufacturing challenges. accelerates innovation in the global electronics market. It seems that the tool enables retiming and pipelining register where as I ordered from the project file a disable of any retiming using the following setoptions command: device options. In this tab, the user must include the path to needed libraries under 'Include Path Order.' Click on the + file icon to add the directory path and select from the ACEinstallation path as shown below.

SYNPLIFY PRO PRO

The Synplify Pro and Synplify Premier FPGA design tools provide additional value by offering links to high-performance functional verification with VCS simulation and integration with Synphony Model Compiler for high-level synthesis of signal processing hardware. Hi, I have some problems using Synplify Pro v8.8 for my FPGA design flow. Synplify Pro propagates this value throughout the design.

SYNPLIFY PRO SOFTWARE

So what should i do in order that the tool does not remove this register (which is really important in my design btw).Synopsys, Inc., a world leader in software and IP used in the design, verification and manufacture of electronic components and systems, has released K-2015.09 version of Synplify, is provides a high-quality, high-performance, and easy-to-use FPGA implementation and debug environment.ĭesigners using Synopsys’ FPGA tool suite gain fast time-to-results for complex FPGAs, area optimization for both cost and power reduction, automation for soft error mitigation, hierarchical design capabilities and multi-FPGA vendor support. Reg clk_bit_o /* synthesis syn_preserve = 1 */ U_ww.u_New registers created by retiming :īesides, I added into the code a synthesis macro in order to preserve the corresponding register from any eventual retiming using the following definition: Original and Pipelined registers replaced by retiming :

SYNPLIFY PRO MANUAL

Retiming summary : 2 registers retimed to 20 Synopsys FPGA Synthesis Products H-2013.03 Synopsys FPGA Synthesis Products H-2013.03 1.0 Gb Synopsys, Inc. Synplify Pro Reference Manual February 2004 Synplicity, Inc. Synopsys Synplify P-2019. Application Note Synplify Tool RAM Inferencing Support To infer a RAM, the Synplify synthesis tool lo oks for an assignment to a signal (register in Verilog) that is an array of an array, or a case structure controlled by a clock edge and a write enable.

Synplify software supports the latest VHDL and Verilog language constructs including SystemVerilog and VHDL-2008. has unveiled Synplify P-2019.03-SP1 synthesis software tools is the industry standard for producing high-performance and cost-effective FPGA designs. RAM Inferencing in Synplify Software Using Xilinx RAMs Synplicity, Inc. Synplify Synplify® FPGA synthesis software is the industry standard for producing high-performance and cost-effective FPGA designs.

SYNPLIFY PRO UPDATE

back in Diamond, Design->Refresh Design to update status. Synopsys Synplify P-2019.03-SP1 Synopsys, Inc.

Set_option -default_enum_encoding defaultĭespite this, it seems that the tool retimed some registers: (which opens Synplify with the project sources) - hit 'RUN' in Synplify. It seems that the tool enables retiming and pipelining register where as I ordered from the project file a disable of any retiming using the following set_options command: I have some problems using Synplify Pro v8.8 for my FPGA design flow.

0 kommentar(er)

0 kommentar(er)